组成

计算机的总线

- 总线的概述

- 总线可以解决的问题

- 提供了对外连接的接口

- 不同设备可以通过物理接口进行连接

- 连接的标准,促使外围设备接口的统一

- 解决不同设备之间的通信问题

- 总线的分类

- 片内总线

- 芯片内部的总线

- 寄存器与寄存器之间连接

- 寄存器与控制器、运算器之间连接

- 高集成度芯片内部的信息传输线

- 系统总线

- 数据总线

- 双向传输各个部件的数据信息

- 数据总线的位数(总线宽度)是数据总线的重要参数

一般与CPU位数相同(32位、64位)

- 地址总线

- 指定源数据或目的数据在内存中的地址

- 地址总线的位数与存储单元有关

地址总线位数 = n,寻址范围:0 ~ 2 ^ n

- 控制总线

- 控制总线是用来发出各种控制信号的传输线

- 控制信号经由控制总线从一个组件发给另一个组件

- 控制总线可以监视不同组件之间的状态(就绪/未就绪)

CPU、主内存、IO设备、各组件之间的信息传输线

- 数据总线

- 片内总线

- 总线可以解决的问题

- 总线的仲裁

- 为什么需要仲裁

- 目的是为了解决总线使用权的冲突问题

- 总线仲裁的方法

- 链式查询

- 好处:电路复杂度低,仲裁方式简单

- 坏处:优先级低的设备难以获得总线使用权

- 坏处:对电路故障敏感

- 计时器定时查询

- 仲裁控制器对设备编号并使用计数器累计计数

- 接收到仲裁信号后,往所有设备发出计数值

- 计数值与设备编号一致则获得总线使用权

- 独立请求

- 每个设备均有总线独立链接仲裁器

- 设别可单独向仲裁器发送请求和接收请求

- 当同事收到多个请求信号,仲裁器有权按优先级分配使用权

- 好处:响应速度快,优先顺序可以动态改变

- 坏处:设备连线多,总线控制复杂

- 链式查询

- 为什么需要仲裁

计算机的输入输出设备

- 常见的输入输出设备

- 输入输出的接口通用设计

- CPU 与 IO设备的通信

计算机存储器概览

- 存储器按照介质的分类

- 半导体存储器

- 磁存储器

- 存储器按照存取方式分类

- 随机存储器RAM

- 随机读取

- 与位置无关

- 串行存储器

- 与位置有关

- 按顺序查找

- 只读存储器ROM

- 只读不写

- 随机存储器RAM

- 存储器的层次结构

容量 + 价格 => 位价:每比特位价格- 缓存

- 主存

- 辅存

计算机的主存储器与辅助存储器

- 主存储器

- 内存

- RAM(随机存储器:Random Access Memory)

- RAM通过电容存储数据,必须隔一段时间刷新一次

- 如果掉电,那么一段时间后将丢失所有数据

- 32位系统 2 ^ 32 = 4 x 2 ^ 30 = 4GB,最大支持4GB内存

- 64位系统 2 ^ 64 = 2 ^ 34 x 2 ^ 30 = 2 ^ 34GB,最大支持2 ^ 34GB内存

- 内存

- 辅助存储器

- 磁盘

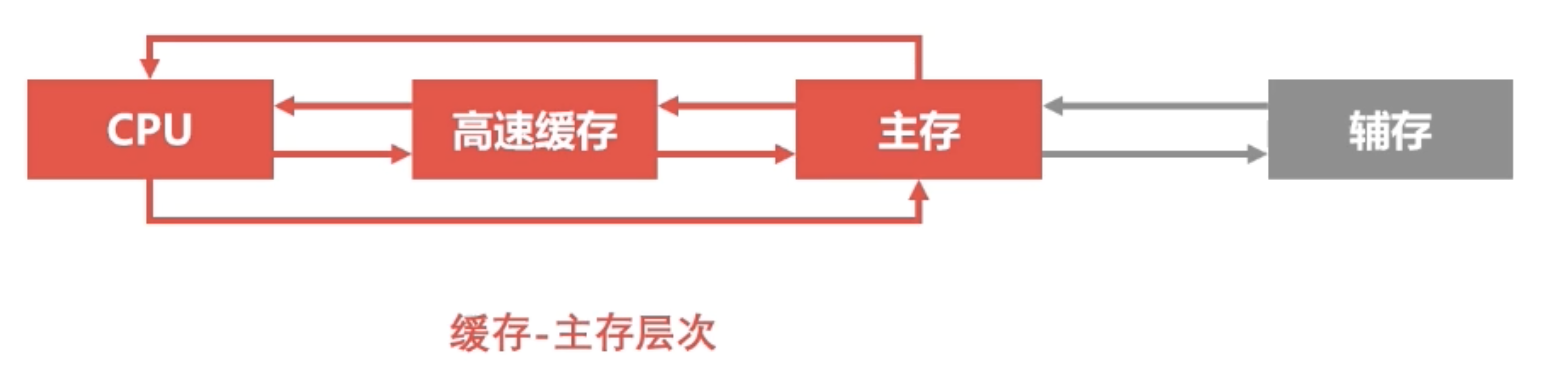

计算机的高速缓存

-

高速缓存的工作原理

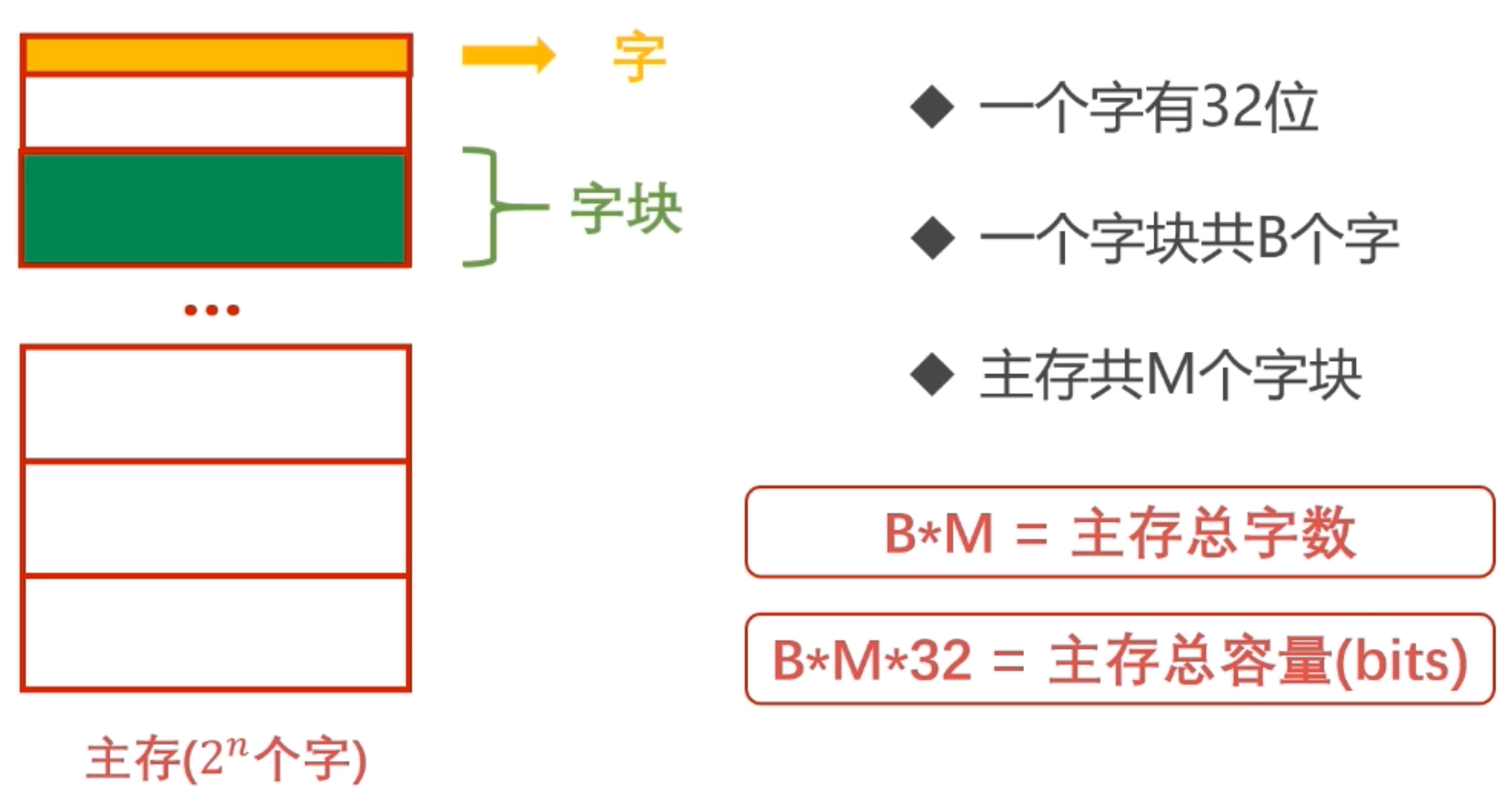

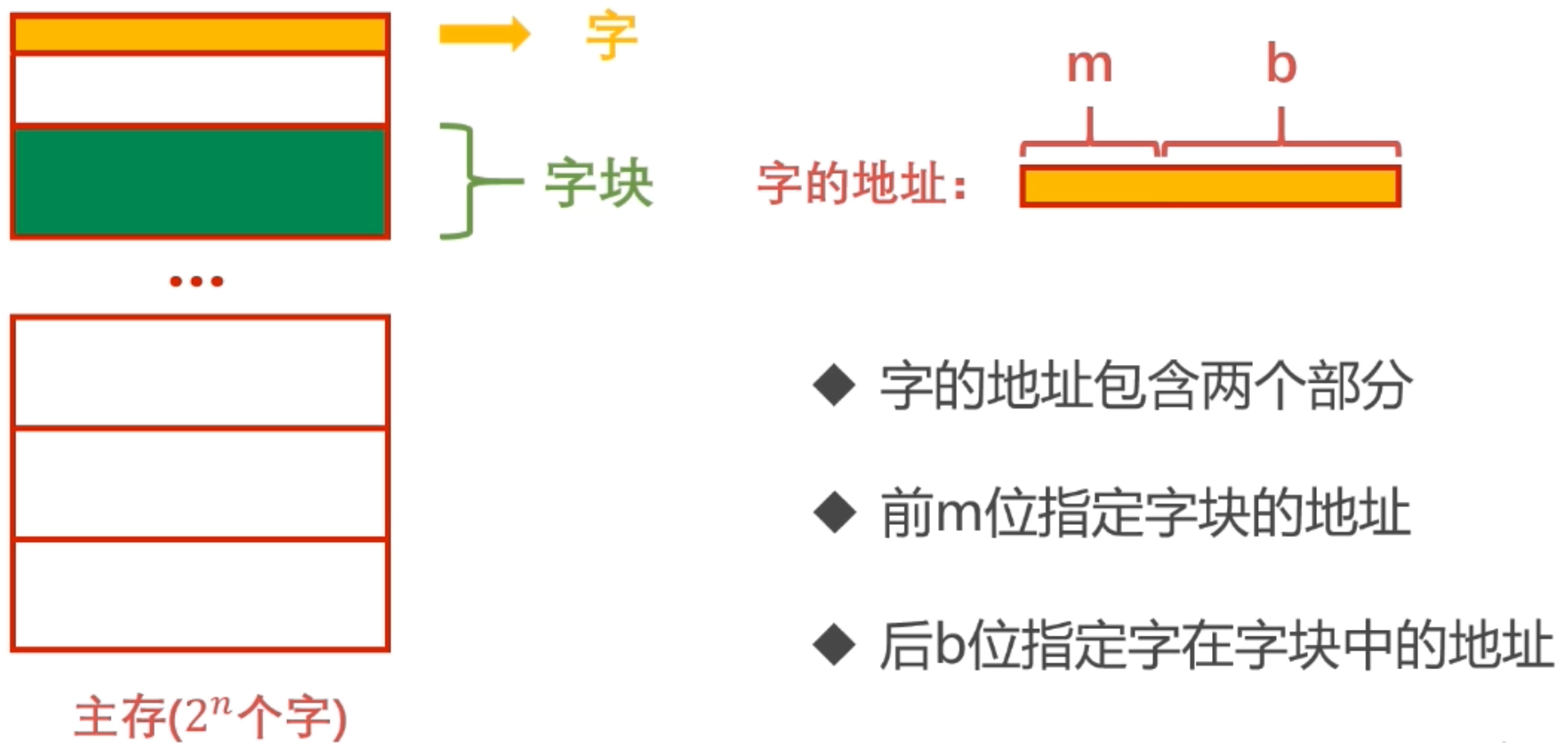

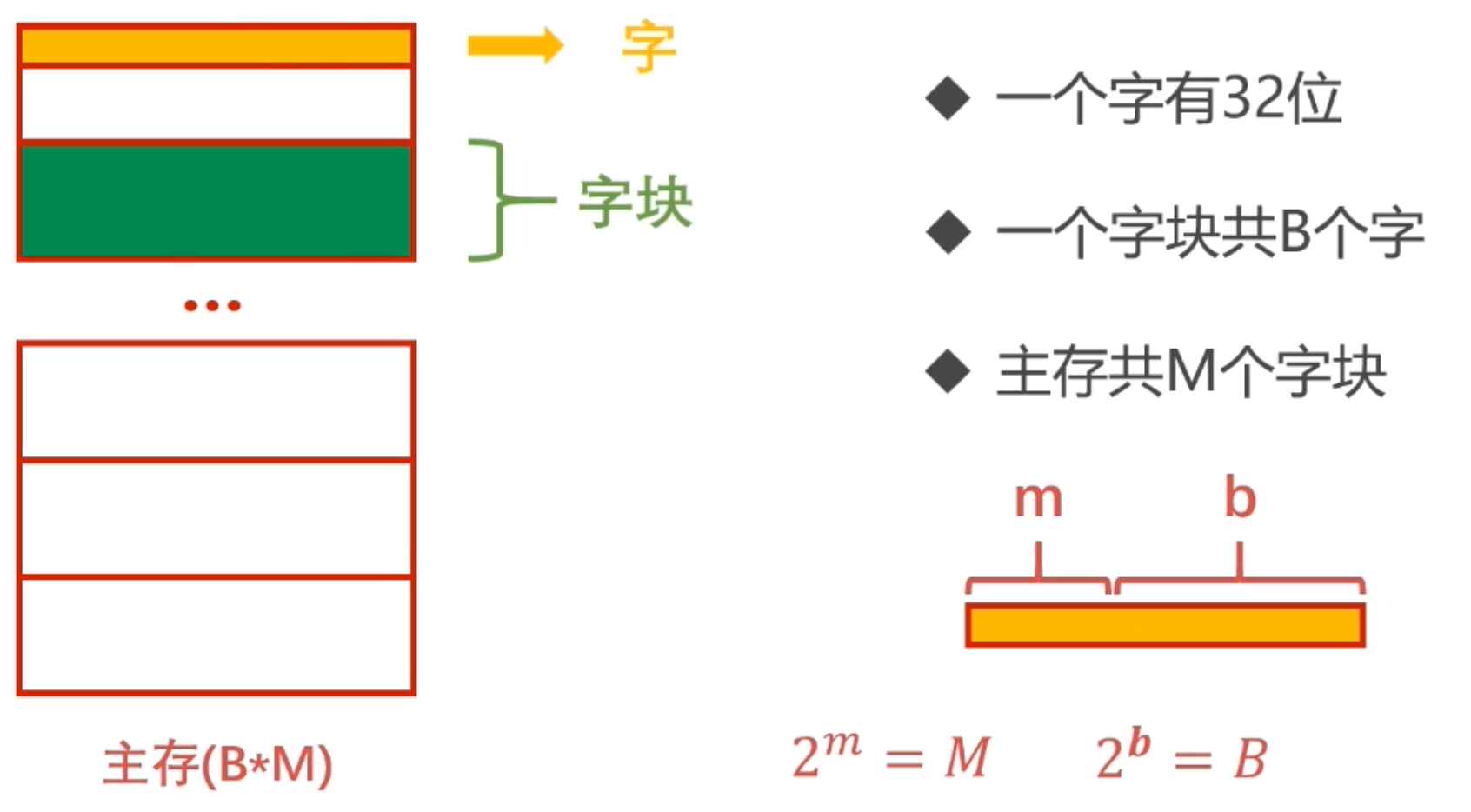

- 字:是指存放在一个存储单元中的二进制代码组合(一个字可以代表一个数据、可以表示一个指令、或者表示一个字符串,字 是内存当中存储的最小单位)

- 字块:存储在连续的存储单元中而被看作是一个单元的一组字(字块是包含了多个字)

- 字 与 字块的运算

- B * M = 主存总字数

- B * M * 32(假设值) = 主存总容量(bits)

- 有了字块与字的概念,就可以衍生出寻址的概念了。

寻址基础 - 例子:假设主存用户空间容量为4G,字块大小为4M,字长为32位,则对于字地址中的块地址m和块内地址b的位数,至少应该是多少?

- 解:4G = 4096

- 字块数:4096 / 4 = 1024

- 字块地址m:log2 1024 = 10(在地址里面至少需要10位来表示1024个字块)

- 块内字数:4M / 32bit = 1048576(每个字块里面有1048576个字)

- 块内地址b:log2 1048576 = 20(至少需要20位的块内地址来表示块内所有的字)

- 结论:m >= 10, b >= 20

- 拓展知识

- 主存容量要比缓存容量大

- 主存与缓存的存储结构类似,也是有字和字块的概念

- 缓存的容量较小

- 缓存的速度更快

- 缓存命中率:CPU需要的数据不在缓存里,需要去主存拿,但是CPU从主从拿数据会降低响应时间,所以尽可能的还是从缓存读取数据,从缓存读取成功/失败则可计算出缓存的命中率

- 命中率是衡量缓存的重要性能指标

- 理论上CPU每次都能从高速缓存取数据的时候,命中率为1

- 访问主存次数 Nm,访问cache次数Nc,则命中率为 h = Nc / Nm + Nc

- 访问效率:e

- 访问主存时间 Tm,访问缓存时间 Tc,访问Cache-主存系统平均时间:Ta = h * Tc + (1 - h) tm

- 访问效率 e = Tc / Ta = Tc / h * Tc + (1 - h)Tm

- 例子:假设CPU在执行某段程序时,共访问了Cache命中2000次,访问主存50次,已知Cache的存取时间为50ns,主存的存取时间为200ns,求Cache-主存系统的命中率、访问效率和平均访问时间

- 命中率: h = Nc / Nc + Nm = 2000 / 2000 + 50 = 0.97

- 访问效率:e = Tc / Ta = Tc / H * Tc + (1 - h)Tm

- = 50 / 0.97 * 50 + (1 - 0.97) * 200 = 0.917 = 91.7%

- 访问时间:0.97 * 50 + (1 - 0.97)* 200 = 54.5ns

- 总结两个公式

- 命中率: h = Nc / Nc + Nm

- 访问效率: e = Tc / Ta = Tc / h * Tc + (1 - h) * Tm

-

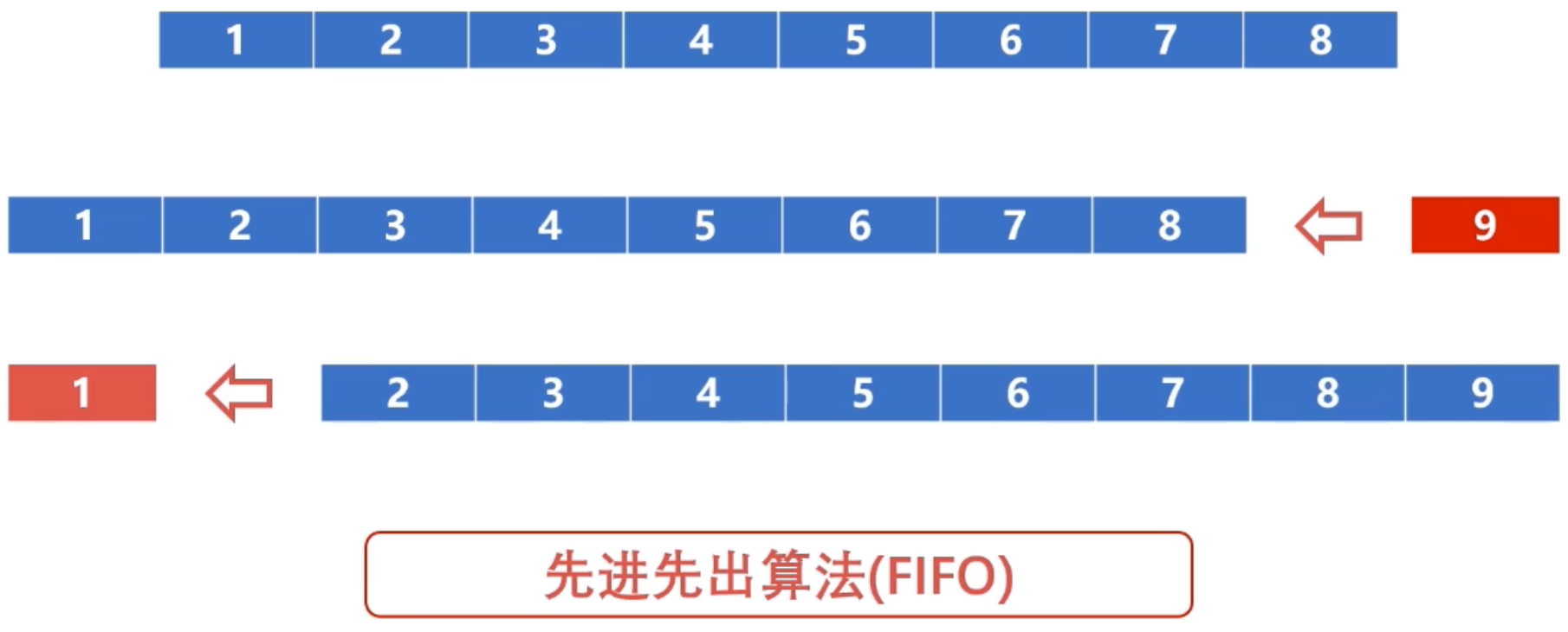

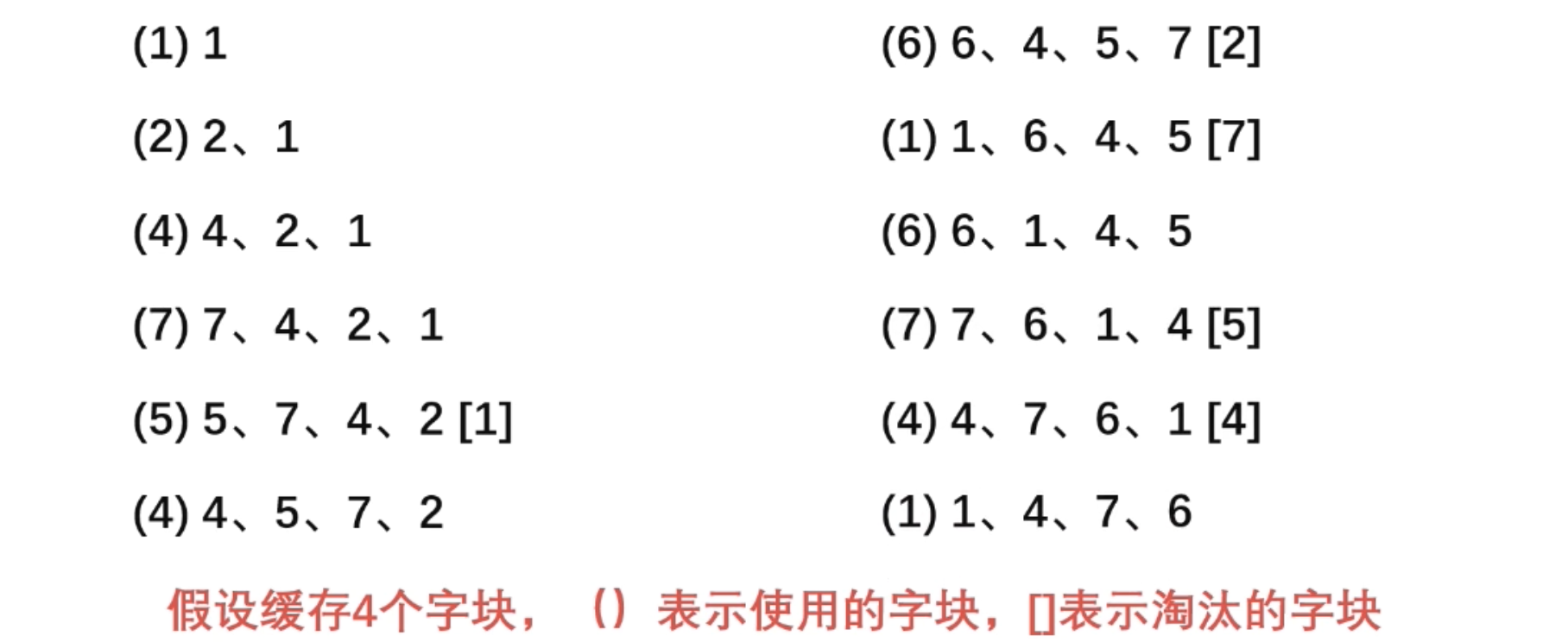

高速缓存的替换策略(高速缓存的替换时机:当CPU需要的数据高速缓存中没有的时候,需要从主存载入所需的数据。这个时候就需要从主存中将数据拿出来 放到高速缓存中去。)

计算机的指令系统

- 机器指令的形式

- 机器指令主要由两部分组成:操作码、地址码

- 操作码指明指令所要完成的操作

- 操作码的位数就反映了机器的操作种类,假设操作码有8位,那么最多就有2^8 = 256种操作

- 地址码直接给出操作数或者操作数的地址

- 分三地址码指令、二地址码指令、一地址码指令、零地址指令(分别表示地址码中有N个地址)

- 三地址码示例:

[[操作码][[addr1][addr2][addr3]]],例如1 + 1 = 2对应则为addr1、addr2、addr3 - 二地址码示例:

[[操作码][[addr1][addr2]]],例如1 + 1 = 2对应则为addr1、addr2,结果在addr1 或 addr2 - 一地址码示例:

[[操作码][[addr1]]],可以理解为自己对自己的操作,或者自增的操作。不需要别的参数或行为 - 零地址指令:在机器指令中无地址码,一般会是空操作、停机操作、中断返回等操作

- 三地址码示例:

- 机器指令主要由两部分组成:操作码、地址码

- 机器指令的操作类型

- 数据传输:

- 寄存器之间、寄存器与存储单元、存储单元之间传送

- 数据读写、交换地址数据、清零置一等操作

- 算术逻辑操作

- 操作数之间的加减乘除

- 操作数的与或非等逻辑位运算

- 移位操作

- 数据左移(乘 2)、数据右移(除 2)

- 完成数据在算术逻辑单元的必要操作

- 控制指令

- 等待、停机、空操作、中断等指令

- 数据传输:

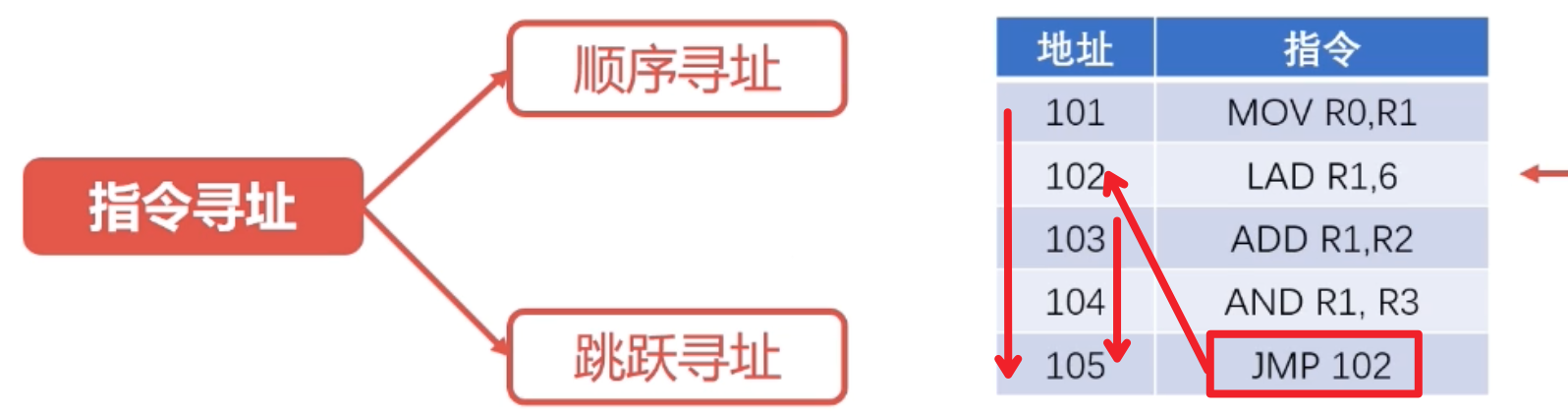

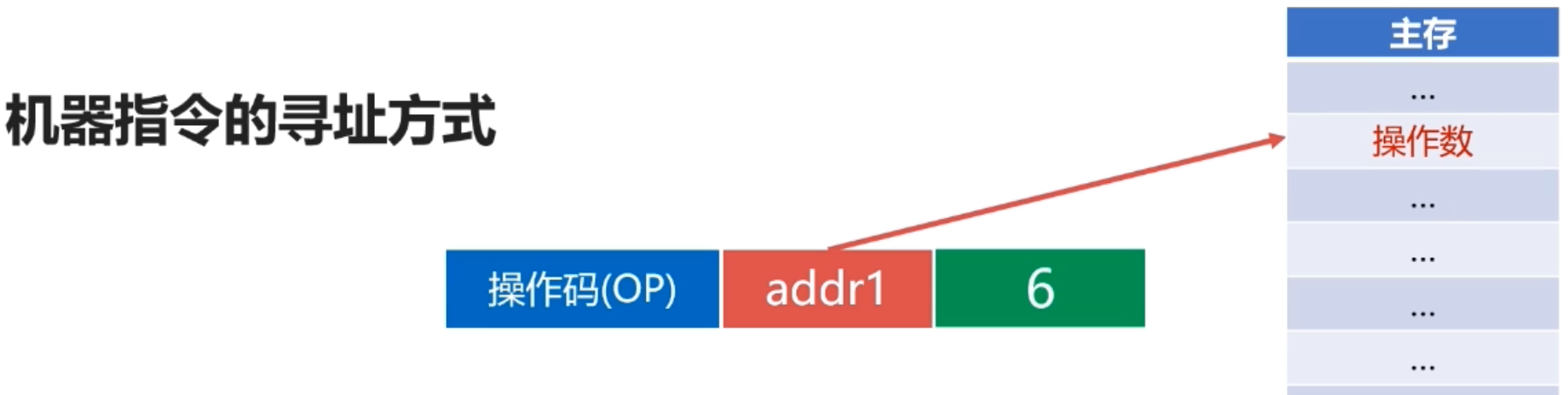

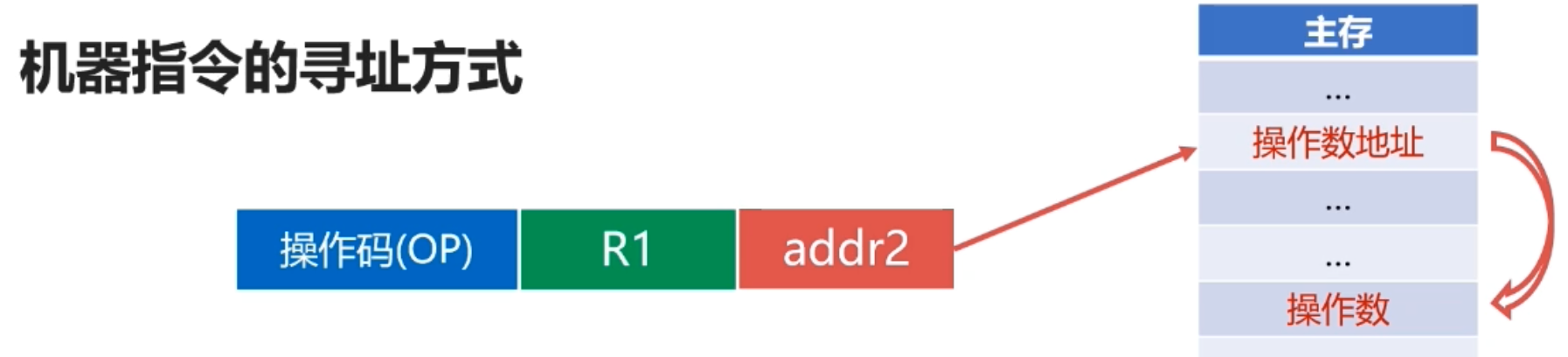

- 机器指令的寻址方式

计算机的控制器

- 控制器是协调和控制计算机运行的

- 控制器包含

- 程序计数器

- 用来存储下一条指令的地址

- 循环从程序计数器中拿出指令

- 当指令被拿出时,指向下一条指令

- 时序发生器

- 电气工程领域,用于发送时序脉冲

- CPU依据不同的时序脉冲有节奏的进行工作

- 指令译码器

- 控制器的主要部件之一

- 计算机指令由操作码和地址码组成

- 翻译操作码对应的操作以及控制传输地址码对应的数据

- 各种寄存器

- 指令寄存器

- 是控制器的主要部件之一

- 从主存或高速缓存取计算机指令

- 主存地址寄存器

- 保存当前CPU正要访问的内存单元的地址

- 主存数据寄存器

- 保存当前CPU正要读或写的主存数据

- 通用寄存器

- 用于暂时存放或传送数据或指令

- 可保存ALU的运算中间结果

- 容量比一般专用寄存器要大

- 指令寄存器

- 总线

- 程序计数器

- 控制器包含

计算机的运算器

- 运算器是用来进行数据运算加工的

- 运算器包含

- 数据缓冲器

- 分为输入缓冲和输出缓冲

- 输入缓冲暂时存放外设送过来的数据

- 输出缓冲暂时存放送往外设的数据

- ALU

- 算术逻辑单元,是运算器的主要组成

- 常见的位运算(左右移、与或非等)

- 算术运算(加减乘除等)

- 通用寄存器

- 用于暂时存放或传送数据或指令

- 可保存ALU的运算中间结果

- 容量比一般专用寄存器要大

- 状态字寄存器

- 存放运算状态(条件码、进位、溢出、结果正负等)

- 存放运算控制信息(调试跟踪标记位、允许中断位等)

- 总线

- 数据缓冲器

- 运算器包含